# Performance of Three Phase 11-level Inverter with reduced number of switches using different PWM Techniques

Rahul Nair, M.Tech student, Department of Electrical Engg, Amrita Vishwa Vidyapeetham, Bangalore, India- 560 035. Email:rahulnairmails@gmail.com Mahalakshmi R, Assistant Professor, Department of Electrical Engg, Amrita Vishwa Vidyapeetham, Bangalore, India- 560 035. Dr. Sindhu Thampatty K.C., Professor, Department of Electrical Engg, Amrita Vishwa Vidyapeetham, Coimbatore, India- 641112.

Abstract—As compared to conventional inverter topologies like diode clamped and capacitor clamped inverters, the cascaded multilevel inverter has lesser harmonics as well as lower switching stress. The cascaded topology has more number of power switches leading to greater heat losses, larger size, higher cost and more gate drive circuitry. The proposed configuration contains less number of switches and produces lesser harmonics in the output voltage than the cascaded topology. A comparison between four different types of pulse width modulation (PWM) techniques, namely, In-phase disposition (IPD), Anti-phase disposition (APD), Carrier Overlap (CO) and Variable Frequency (VF) PWM methods, has been done. The results have been verified through simulation study in MATLAB/Simulink in order to select the best PWM method that provides minimum THD in the output voltage. An LC filter has been designed to improve the harmonic profile.

Keywords: Multilevel inverter, PWM technique, total harmonic distortion, LC filter.

#### I. INTRODUCTION

Power electronic devices play a major role in the conversion and control of electric power, especially to extract power from renewable energy sources like photovoltaic array and wind energy [1]. Conversion of DC to AC power can be done with the help of inverters (single phase or three phases). Conventional bipolar inverters produce alternating staircase waveforms with higher harmonics. Thus, the multilevel inverters (MLI) were developed [2]. This paper provides a new three phase configuration to produce the 11-level output with less total harmonic distortion (THD) in its output voltage. IPD, APD, CO and VF PWM techniques were used to produce

switching pulses[3].

The cascaded H-bridge (CHB) configuration has lesser number of components as compared to the conventional diode clamped or capacitor clamped inverters [4]. It contains single phase inverters connected in series with separate DC sources that can be derived from renewable energy sources like solar PV cell, bio fuel cell or wind turbine [5]. Each single phase inverter produces two DC voltage levels. Bridges with separate DC sources are cascaded to each other for more DC levels. The switches operate at fundamental frequency of 50Hz.

The diode clamped MLI has 20 switches, 90 diodes and 10 main DC-bus capacitors per phase to produce an 11level staircase as the output voltage. The capacitor clamped MLI uses 20 switches, 45 clamping capacitors and 10 main DC-bus capacitors per phase whereas the cascaded H-bridge inverter uses only 24 switches per phase to produce the same output [6-7]. This paper describes a single phase inverter configuration with eight switches and three DC sources. A three phase multilevel inverter is obtained by interconnecting three single phase inverters to a star connected pure resistive load with a common earth point. Therefore, this circuit offers lesser gate control circuitry, lesser cost, lesser heating, more ease of installation and lesser electromagnetic interference. Table.1 shows the comparison of the number of components between different topologies. The performance of the inverter using IPD, APD, CO and VF PWM methods is shown [8]. A passive series LC filter is designed to produce a sine wave from the staircase inverter output. The purpose of the output LC filter is attenuating voltage ripples due to the inverter switching [9].

This paper is organised into many sections. Section II contains the circuit configuration and its modes of operation. Section III mentions some modulation schemes available for switching of the inverter. The simulation results are analysed in section IV. The waveform obtained after implementing the series LC filter at the inverter output is analysed in section V. Section VI gives the conclusion.

Number Of Components Per Phase For Different

11-Level Inverter Topologies

| Sl.No. | Configuration         | Number of<br>switches per<br>phase | Number of conducting switches per phase |

|--------|-----------------------|------------------------------------|-----------------------------------------|

| 1      | Diode Clamped         | 20                                 | 4                                       |

| 2      | Capacitor Clamped     | 20                                 | 4                                       |

| 3      | Cascaded H-<br>Bridge | 24                                 | 14                                      |

| 4      | Eight switch type     | 8                                  | 4                                       |

## II. PROPOSED TOPOLOGY AND ITS OPERATION

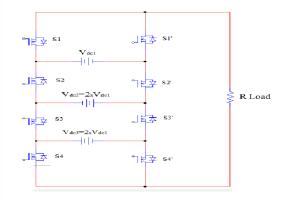

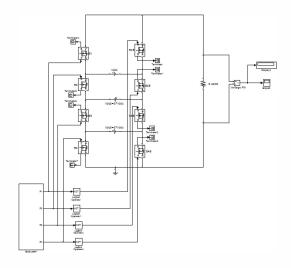

The proposed inverter configuration has eight switches and three DC sources per phase as shown in Fig.1. The series combination among the three DC sources Vdc, 2Vdc and 2Vdc can be used to produce eleven DC levels at the inverter output in a single cycle. Fig.2 provides the simulation circuit of the proposed single phase circuit in MATLAB. In each mode, four of the switches operate simultaneously.

Fig.1. Proposed configuration for single phase Inverter operation

Fig.2. Simulation Circuit of the proposed Inverter Configuration

TABLE.2

#### SWITCHING STATES IN 11-LEVEL INVERTER

| Output             | S1 | S2 | S3 | S4 | S1B | S2B | S3B | S4B |

|--------------------|----|----|----|----|-----|-----|-----|-----|

| Voltage            |    |    |    |    |     |     |     |     |

| +5V <sub>dc</sub>  | 1  | 0  | 1  | 0  | 0   | 1   | 0   | 1   |

| +4 V <sub>dc</sub> | 0  | 0  | 1  | 0  | 1   | 1   | 0   | 1   |

| +3 V <sub>dc</sub> | 1  | 0  | 1  | 1  | 0   | 1   | 0   | 0   |

| +2 V <sub>dc</sub> | 0  | 0  | 1  | 1  | 1   | 1   | 0   | 0   |

| + V <sub>dc</sub>  | 1  | 0  | 0  | 0  | 0   | 1   | 1   | 1   |

| 0                  | 0  | 0  | 0  | 0  | 1   | 1   | 1   | 1   |

| - V <sub>dc</sub>  | 0  | 1  | 1  | 1  | 1   | 0   | 1   | 1   |

| -2 V <sub>dc</sub> | 1  | 1  | 0  | 0  | 0   | 0   | 1   | 1   |

| -3 V <sub>dc</sub> | 0  | 1  | 0  | 0  | 1   | 0   | 1   | 1   |

| -4 V <sub>dc</sub> | 1  | 1  | 0  | 1  | 0   | 0   | 1   | 0   |

| -5V <sub>dc</sub>  | 0  | 1  | 0  | 1  | 1   | 0   | 1   | 0   |

| 0                  | 1  | 1  | 1  | 1  | 0   | 0   | 0   | 0   |

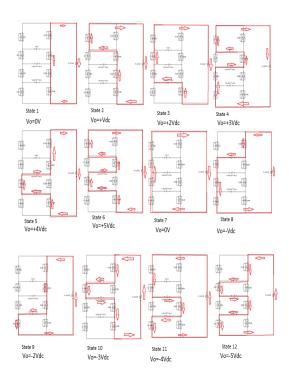

Fig.3 shows the conducting switches at different operating states.  $+V_{dc}$  level voltage is obtained by turning on

the switches S1, S2B, S3B and S4B together. Similarly, all the DC output voltage levels are obtained as shown in TABLE.2.

Fig.3. States corresponding to each Output voltage level

#### III. MODULATION SCHEMES

To control the frequency and harmonics of the output voltage of the inverter, we must select the most appropriate PWM technique. The sinusoidal PWM (SPWM) method has been applied to the power switches, in which a reference sinusoidal wave of fundamental frequency is compared to high frequency carrier wave(s). The level, frequency or amplitude of the multiple carrier signals are varied based on the PWM technique. The modulation indices are kept same in all the methods for comparison. Amplitude modulation index is the ratio of the amplitude of the reference sine wave to the amplitude of the carrier waves. Frequency modulation index, is defined as the ratio of the frequency of carrier wave to the frequency of the modulating wave. Amplitude modulation index  $m_a$  and frequency modulation index  $m_f$  are given by (1) and (2) respectively.

$$m_a = A_m / A_c \tag{1}$$

$$m_f = f_c / f_m \tag{2}$$

The PWM techniques discussed in this paper are In-Phase Disposition (IPD) type level shift pulse width modulation (LS-PWM), Anti-Phase Disposition (APD) PWM, Carrier Overlap (CO) PWM and Variable Frequency (VF) PWM. The amplitude modulation index  $m_a$  is maintained at 0.9 and the frequency modulation index  $m_f$  at 200. The RMS value of the fundamental component of the output voltage and the total harmonic distortion (THD) are observed by using simulation results. In all the PWM techniques, 'N' number of carrier signals are used to obtain 2N+1 voltage levels.

## A. In-Phase Disposition Level-Shift PWM (IPD-LSPWM) Method

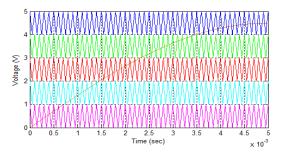

The carrier signals are level shifted in this PWM technique. They have the same amplitude of 1V and a frequency of 10kHz. The level shifted carrier signals are compared with a diode bridge rectified reference sine wave which is at fundamental frequency, as illustrated in Fig.4. The different levels of the output wave is detected and decoded to produce the pulses required to trigger each switch in the inverter. In order to obtain a three phase inverter, the sine wave is phase shifted by 120°.

Fig.4. Reference Sine wave and Carrier waves for IPD-LSPWM at ma=0.9 and mf=200.

### B. Anti-Phase Disposition Level-Shift PWM (APD-LSPWM) Method

Each carrier signal is out of phase with neighbouring carrier signals by  $180^{\circ}$  and have the same amplitude and frequency. The carrier signals are compared with the reference sine wave (which is at fundamental frequency) to produce required gate pulses as shown in Fig.5.

Fig.5. Reference Sine wave and Carrier waves for APD-LSPWM at  $m_a$ =0.9 and  $m_f$ =200.

#### C. Carrier Overlap PWM (CO-PWM) Method

This strategy utilizes level shifted carrier waves of the same frequency and amplitude. They are in phase with each other and also overlap each other. They are compared to a diode bridge rectified reference sine wave in Fig.6 in order to produce the gate pulses.

Fig.6. Reference Sine wave and Carrier waves for CO-PWM method at ma=0.9 and mf=200.

#### D. Variable Frequency PWM (VF-PWM) Method

In Fig.7, all the level-shifted carrier waves have the same amplitude. The lowermost carrier wave has very high frequency, 10kHz followed by 8kHz, 6kHz, 4kHz and the uppermost carrier signal has lowest frequency, 2kHz. They are compared with the reference sine wave with fundamental frequency to produce required switching pulses.

Fig.7. Reference Sine wave and Carrier waves for VF-PWM at ma=0.9

#### IV. SIMULATION RESULTS & DISCUSSION

Various PWM techniques are applied to the proposed three phase inverter topology at the same amplitude and frequency modulation indices using MATLAB/ Simulink. A comparative study has been made between the RMS values of fundamental value of the output voltage and the total harmonic distortion for a single phase using the Fast Fourier Transform (FFT) block. The circuit parameters used are:

$$f_c = 10 \text{kHz}$$

;  $f_m = 50 \text{Hz}$ ;  $A_m = 4.5 \text{V}$ ;  $A_f = 5 \text{V}$ .

Star connected resistance load (R = 50 $\Omega$ )

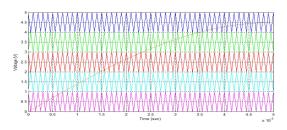

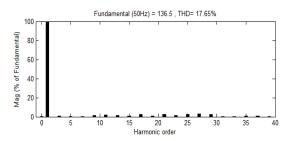

The three phase output voltage waveform obtained from IPD-LSPWM method is shown in Fig.8. It has significant 11<sup>th</sup>, 17<sup>th</sup>, 21<sup>st</sup>, 25<sup>th</sup>, 27<sup>th</sup> and 29<sup>th</sup> harmonic values as given by its FFT analysis in Fig.9. The fundamental value of output voltage is higher and the THD is lesser in the IPD type LS-PWM than the APD type. The carrier waves are in phase with each other in the IPD type, resulting in less complex circuitry.

Fig.8. Output voltage waveform for three phase 11 level Inverter using IPD-LSPWM technique.

Fig.9. FFT Analysis of the harmonic spectrum for IPD-LSPWM technique

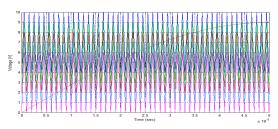

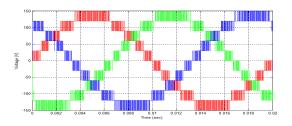

The output voltage and the FFT analysis for APD-LSPWM technique are shown in Fig.10 and 11 respectively. The 17<sup>th</sup>, 21<sup>st</sup>, 23<sup>rd</sup>, 25<sup>th</sup>, 27<sup>th</sup> ad 29<sup>th</sup> harmonics are significant.

Fig. 10. Output voltage waveform for three phase 11 level Inverter using APD-LSPWM technique.

Fig.11. FFT Analysis of the harmonic spectrum for APD-LSPWM technique

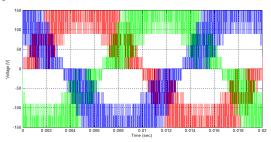

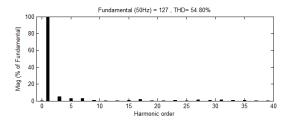

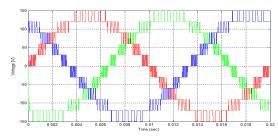

Fig.13 provides the FFT analysis of the output voltage of CO-PWM method is shown in Fig 12. The 3<sup>rd</sup>, 5<sup>th</sup>, 7<sup>th</sup> and 17<sup>th</sup> harmonics have higher energy. The output produced by CO-PWM has highest THD of 54.80% and lowest RMS value of fundamental output voltage of 127V among the four methods. This method produces pulses that overlap each other. Hence, the resultant voltage waveform has very high THD, which is not close to the sine wave. The carrier waves have larger amplitudes than other PWM techniques.

Fig.12. Output voltage waveform for three phase 11 level Inverter using CO-PWM technique.

Fig.13. FFT Analysis of the harmonic spectrum for CO-PWM technique

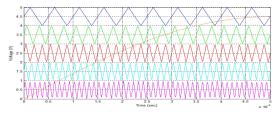

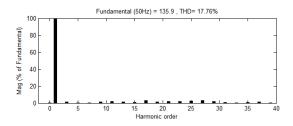

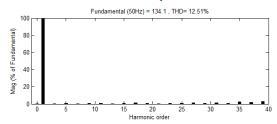

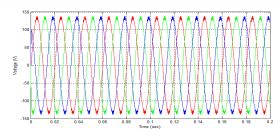

The FFT of the inverter output voltage in Fig.14 from the VF-PWM method is demonstrated in Fig.15. The THD obtained through this method is only 12.51%. The spectrum has more 17<sup>th</sup>, 37<sup>th</sup> and 39<sup>th</sup> harmonic energy.

Different carrier frequencies are used in this method, resulting in utilization of more analog components and large circuitry. The size and cost of the circuit can be reduced by opting for digital pulse generation, by using a suitable microcontroller kit.

Fig.14. Output voltage waveform for three phase 11 level Inverter using VF-PWM technique.

Fig.15. FFT Analysis of the harmonic spectrum for VF-PWM technique

The performance analysis of the three phase inverter based on the THD of the output voltage is given in Table.3. VF-PWM technique was found to be providing minimum harmonics in the output voltage among the four types.

$V_{\text{RMS}} \, (\text{Fundamental}) \, \text{And Thd Of Output Voltage For} \\ \text{Chosen Topology For Different Pwm Techniques}$

| Sl.No. | PWM<br>Technique | RMS Value of<br>Fundamental of<br>Output Voltage (in<br>Volts) | THD (in %) |

|--------|------------------|----------------------------------------------------------------|------------|

| 1      | IPD-<br>LSPWM    | 136.5                                                          | 17.65      |

| 2      | APD-<br>LSPWM    | 135.9                                                          | 17.76      |

| 3      | CO- PWM          | 127                                                            | 54.80      |

| 4      | VF- PWM          | 134.1                                                          | 12.51      |

#### V. OUTPUT AFTER USING AN LC FILTER

An L-C filter is connected at the output of the inverter to produce a sinusoidal waveform with reduced THD. The L and C values are designed to maintain the switching ripple current under the target value. The inductance value is thus given by:

$$L \ge \frac{R_{L-max}}{3\omega} \text{ for single phase}$$

(3)

and

$$L \ge \frac{2*R_{L-max}}{p(p^2-1)\omega} \text{ for polyphase}$$

(4)

(where p=number of phases and  $\omega=2\pi f$ ).

The three phase inverter is connected to a star connected pure resistance load of  $50\Omega$ . The capacitance value of the filter is assumed to be  $1\mu F$ .

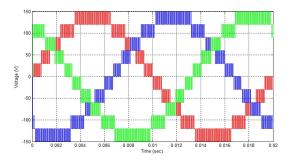

Fig.16. Sinusoidal output voltage waveform for three phase 11 level Inverter using VF-PWM technique with series LC filter.

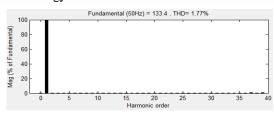

The signal obtained after the LC filter exhibits 1.77% THD. Fig.17 provides the details of the harmonics of the output AC voltage waveform in Fig.16.

Fig.17. FFT Analysis of the harmonic spectrum for VF-PWM technique (with LC filter)

#### VI. CONCLUSION

Three phase eleven level inverter topology with less number of switches is proposed and simulated. Various PWM methods are analyzed and compared.

From the simulation results, it was found that VF-PWM provides minimum THD of 12.51% in the inverter output voltage. This will be the best PWM technique for inverter switching because small inductance can be used in the LC filter placed in series to the inverter output to produce a rectified AC sine wave of low THD of 1.77%.

#### REFERENCES

- [1] Rodriguez J., Lai J.S., Peng F.Z. 'Multilevel inverters: A survey of topologies, controls, and applications'. IEEE Trans. Ind. Electron., vol.49, no. 4, pp. 724–738, Aug. 2002.

- [2] Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Pérez, M.A.; , "A Survey on Cascaded Multilevel Inverters," Industrial Electronics, IEEE Transactions on , vol.57, no.7, pp.2197-2206, July 2010.

- [3] Balamurugan C.R., Natarajan S.P., Vidhya V. A New Modified Hybrid H-Bridge Multilevel Inverter using less Number of Switches'. International Conference on Computation of Power, Energy, Information and Communication (ICCPEIC), 2013, pp 1-6.

- [4] Mohamed A.S, Norman Mariun, Nasri Sulaiman, MAmran M. Radzi: "A New Cascaded Multilevel Inverter Topology with Minimum Number of Conducting Switches," IEEE Innovative Smart Grid Technologies-Asia (ISGT ASIA) 2014.

- [5] Khomfoi S., Praisuwanna N., Tolbert L.M.: "A Hybrid Cascaded Multilevel Inverter Application for Renewable Energy Resources Including a Reconfiguration Technique," Electrical Engineering and Computer Science, The University of Tennessee, USA.

- [6] Salodkar P., Sandeep N., Kulkarni P.S., Ajaykumar R.Y.: 'A Comparison of Seven-Level Inverter Topologies for Multilevel DC-AC Power Conversion'. IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), 2014.

- [7] Beigi L.M.A., Azli N.A., Khosravi F., Najafi E., Kaybhosravi A.: 'A New Multilevel Inverter Topology with less Power Switches', International Conference on Power and Energy, 2012, IEEE , 2-5 December 2012.

- [8] Vadhiraj S., Narayana Swamy K., Divakar B.P.; "Generic SPWM Technique for Multilevel Inverter," Electrical and Electronics Dept, REVA Institute of Technology and Management, Bangalore, India.

- [9] Hyosung Kim, Seung-Ki Sul, "Analysis on Output LC Filters for PWM Inverters", Power Electronics and Motion Control Conference, 17-20 May 2009. IPEMC, 2009. IEEE 6th International, Pp. 384 – 389.